Page 127 - Computer_Science_F5

P. 127

Computer Science This parallel execution significantly register concurrently. Vector registers can

accelerates computations compared to hold an array of data values of the same

processing elements one at a time.

type, like integers, floating-point numbers,

or booleans.

FOR ONLINE READING ONLY

Instruction Stream

Modern processors often provide

special instruction set extensions (ISA

Extensions) specifically designed for

Processing Unit

SIMD operations. These extensions

offer a rich set of instructions optimised

Data Stream Processing Unit efficient manipulation of data elements

Processing Unit

for vector processing, allowing for

within a vector register.

Processing Unit SIMD ISA extensions provide instructions

for performing arithmetic operations

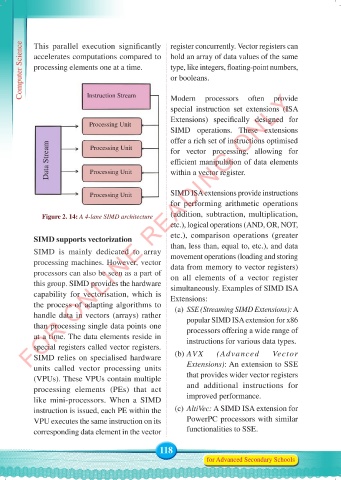

Figure 2. 14: A 4-lane SIMD architecture (addition, subtraction, multiplication,

etc.), logical operations (AND, OR, NOT,

SIMD supports vectorization etc.), comparison operations (greater

SIMD is mainly dedicated to array than, less than, equal to, etc.), and data

movement operations (loading and storing

processing machines. However, vector data from memory to vector registers)

processors can also be seen as a part of on all elements of a vector register

this group. SIMD provides the hardware simultaneously. Examples of SIMD ISA

capability for vectorisation, which is Extensions:

the process of adapting algorithms to (a) SSE (Streaming SIMD Extensions): A

handle data in vectors (arrays) rather popular SIMD ISA extension for x86

than processing single data points one processors offering a wide range of

at a time. The data elements reside in instructions for various data types.

special registers called vector registers.

SIMD relies on specialised hardware (b) AVX (Advanced Vector

units called vector processing units Extensions): An extension to SSE

(VPUs). These VPUs contain multiple that provides wider vector registers

processing elements (PEs) that act and additional instructions for

like mini-processors. When a SIMD improved performance.

instruction is issued, each PE within the (c) AltiVec: A SIMD ISA extension for

VPU executes the same instruction on its PowerPC processors with similar

corresponding data element in the vector functionalities to SSE.

118

for Advanced Secondary Schools

Computer Science Form 5.indd 118 23/07/2024 12:33