Page 64 - Computer_Science_F5

P. 64

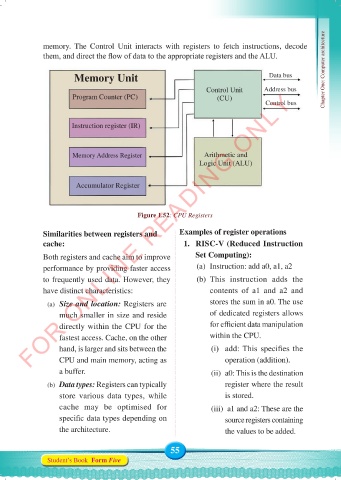

memory. The Control Unit interacts with registers to fetch instructions, decode

them, and direct the flow of data to the appropriate registers and the ALU.

Memory Unit Data bus Chapter One: Computer architecture

Control Unit Address bus

FOR ONLINE READING ONLY

Program Counter (PC) (CU)

Control bus

Instruction register (IR)

Memory Address Register Arithmetic and

Logic Unit (ALU)

Accumulator Register

Figure 1.52: CPU Registers

Similarities between registers and Examples of register operations

cache: 1. RISC-V (Reduced Instruction

Both registers and cache aim to improve Set Computing):

performance by providing faster access (a) Instruction: add a0, a1, a2

to frequently used data. However, they (b) This instruction adds the

have distinct characteristics: contents of a1 and a2 and

(a) Size and location: Registers are stores the sum in a0. The use

much smaller in size and reside of dedicated registers allows

directly within the CPU for the for efficient data manipulation

fastest access. Cache, on the other within the CPU.

hand, is larger and sits between the (i) add: This specifies the

CPU and main memory, acting as operation (addition).

a buffer. (ii) a0: This is the destination

(b) Data types: Registers can typically register where the result

store various data types, while is stored.

cache may be optimised for (iii) a1 and a2: These are the

specific data types depending on source registers containing

the architecture. the values to be added.

55

Student’s Book Form Five

Computer Science Form 5.indd 55 23/07/2024 12:32