Page 48 - Computer_Science_F5

P. 48

When the processor requests data, the two adjacent levels at a time. A block

cache controller first checks the cache. is the fixed-size chunk of data that the

If the data is found, a cache hit occurs, cache transfers between itself and other

and the data is quickly delivered to the memory levels. Chapter One: Computer architecture

processor. If not, a cache miss occurs,

FOR ONLINE READING ONLY

and the cache controller then checks the Cache line: A unit of data storage within

main memory. If the data is found in main the cache. It acts like a container that

memory, a main memory hit occurs, and holds a block and is specifically designed

the data is transferred to the cache and for efficient data transfer between the

then to the processor. If the data is not cache and other memory levels.

in the main memory, a main memory

miss occurs. The data is retrieved from Cache hit: An event in which specific

storage, transferred to the main memory, data or instructions are searched and

then to the cache, and finally delivered found available in the accessed cache

to the processor. memory. In this scenario, the cache

transfers (copies) the requested data to

Cache the processor.

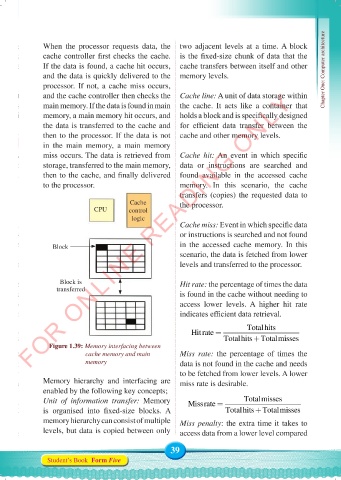

CPU control

logic

Cache miss: Event in which specific data

or instructions is searched and not found

Block in the accessed cache memory. In this

scenario, the data is fetched from lower

levels and transferred to the processor.

Block is Hit rate: the percentage of times the data

transferred

is found in the cache without needing to

access lower levels. A higher hit rate

indicates efficient data retrieval.

Totalhits

Hitrate =

Totalhits+Totalmisses

Figure 1.39: Memory interfacing between

cache memory and main Miss rate: the percentage of times the

memory data is not found in the cache and needs

to be fetched from lower levels. A lower

Memory hierarchy and interfacing are miss rate is desirable.

enabled by the following key concepts;

Unit of information transfer: Memory Missrate = Totalmisses

is organised into fixed-size blocks. A Totalhits+Totalmisses

memory hierarchy can consist of multiple Miss penalty: the extra time it takes to

levels, but data is copied between only access data from a lower level compared

39

Student’s Book Form Five

Computer Science Form 5.indd 39 23/07/2024 12:32