Page 53 - Computer_Science_F5

P. 53

Computer Science (a) Direct mapping

Each block of main memory maps to a single, specific cache line. The formula used is:

Cache line number = (Address of the main memory block)modulo (Total number of lines in cache)

For example: For a cache with 8 lines and a main memory block address of 29, the

FOR ONLINE READING ONLY

calculation is 29 % 8 = 5. Thus, block 29 maps to cache line 5.

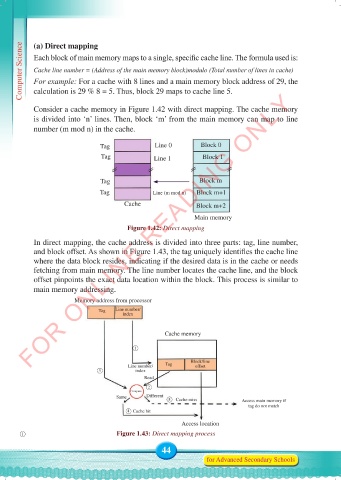

Consider a cache memory in Figure 1.42 with direct mapping. The cache memory

is divided into ‘n’ lines. Then, block ‘m’ from the main memory can map to line

number (m mod n) in the cache.

Tag Line 0 Block 0

Tag Line 1 Block 1

Tag Block m

Tag Line (m mod n) Block m+1

Cache Block m+2

Main memory

Figure 1.42: Direct mapping

In direct mapping, the cache address is divided into three parts: tag, line number,

and block offset. As shown in Figure 1.43, the tag uniquely identifies the cache line

where the data block resides, indicating if the desired data is in the cache or needs

fetching from main memory. The line number locates the cache line, and the block

offset pinpoints the exact data location within the block. This process is similar to

main memory addressing.

Memory address from processor

Tag Line number/

index

Cache memory

1

Line number/ Tag Block/line

offset

3 index

Read

2

Compare

Same Different

5 Cache miss Access main memory if

tag do not match

4 Cache hit

Access location

1 Figure 1.43: Direct mapping process

44

for Advanced Secondary Schools

Computer Science Form 5.indd 44 23/07/2024 12:32