Page 56 - Computer_Science_F5

P. 56

Given the number of blocks in a set = the associativity factor = 8

Cache lines/blocks 2 9

6

Number of sets = = = 2 sets Chapter One: Computer architecture

Number of lines/blocks inaset 8

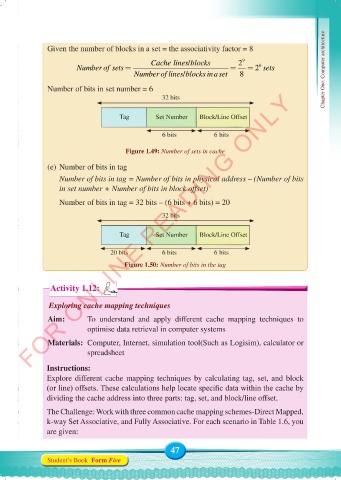

Number of bits in set number = 6

FOR ONLINE READING ONLY

32 bits

Tag Set Number Block/Line Offset

6 bits 6 bits

Figure 1.49: Number of sets in cache

(e) Number of bits in tag

Number of bits in tag = Number of bits in physical address – (Number of bits

in set number + Number of bits in block offset)

Number of bits in tag = 32 bits – (6 bits + 6 bits) = 20

32 bits

Tag Set Number Block/Line Offset

20 bits 6 bits 6 bits

Figure 1.50: Number of bits in the tag

Activity 1.12:

Exploring cache mapping techniques

Aim: To understand and apply different cache mapping techniques to

optimise data retrieval in computer systems

Materials: Computer, Internet, simulation tool(Such as Logisim), calculator or

spreadsheet

Instructions:

Explore different cache mapping techniques by calculating tag, set, and block

(or line) offsets. These calculations help locate specific data within the cache by

dividing the cache address into three parts: tag, set, and block/line offset.

The Challenge: Work with three common cache mapping schemes-Direct Mapped,

k-way Set Associative, and Fully Associative. For each scenario in Table 1.6, you

are given:

47

Student’s Book Form Five

Computer Science Form 5.indd 47 23/07/2024 12:32