Page 93 - Computer_Science_F5

P. 93

Computer Science Meaning of pipelining implementation including those based on RISC and

MIPS principles, often utilise a 5 or 6

an

Pipelining

is

stage pipeline. Here is a breakdown of a

technique in which multiple instructions

common 5-stage pipeline:

are overlapped in execution. A pipeline

is divided into stages and these stages

1. Instruction Fetch (IF): Fetches the

FOR ONLINE READING ONLY

are connected with one another to form

next instruction from memory.

a pipe like structure. Instructions enter 2. Instruction Decode (ID): Decodes

from one end and exit from another the instruction and reads the

end. In a pipelined processor, there are required registers.

two main ends: the input end and the

output end. Between these ends, there 3. Execute (EX): Performs the

are several stages or segments, each arithmetic or logic operation

of which is responsible for a specific specified by the instruction.

operation. The output of one stage 4. Memory Access (MEM): Accesses

connects to the input of the subsequent memory, if necessary, for load or

stage. Interface registers are used to hold store operations.

intermediate output between two stages. 5. Write Back (WB): Writes the result

These interface registers are also known back to the register file.

as latches or buffers.

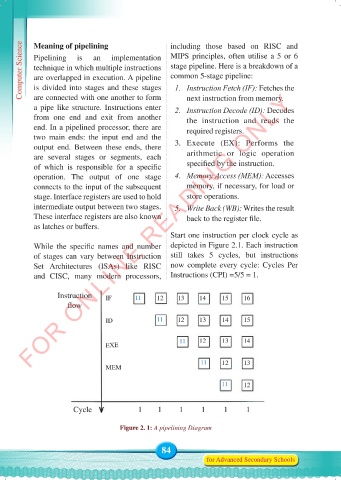

Start one instruction per clock cycle as

While the specific names and number depicted in Figure 2.1. Each instruction

of stages can vary between Instruction still takes 5 cycles, but instructions

Set Architectures (ISAs) like RISC now complete every cycle: Cycles Per

and CISC, many modern processors, Instructions (CPI) =5/5 = 1.

Instruction IF 11 12 13 14 15 16

flow

ID 11 12 13 14 15

11 12 13 14

EXE

11 12 13

MEM

11 12

Cycle 1 1 1 1 1 1

Figure 2. 1: A pipelining Diagram

84

for Advanced Secondary Schools

Computer Science Form 5.indd 84 23/07/2024 12:33