Page 96 - Computer_Science_F5

P. 96

Activity 2.2:

Simulation of the pipeline stages and movement of instruction in Computer

memory and cache using CPU Simulator

Aim: Chapter Two: Performance and optimisation of computer processor

FOR ONLINE READING ONLY

To visualise and understand analysis of LDB instruction in CPU Simulator by

simulating pipeline stages and instruction movement

Material: Computer, CPU simulator software or internet

Instructions:

Conduct a cache performance analysis of LDB Instruction in CPU Simulator by

repeating steps in Activity 2.1 with the LDB values between 0 to 10

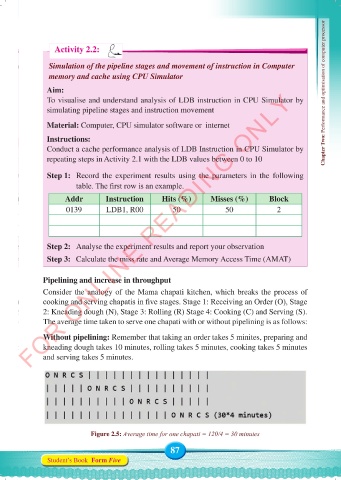

Step 1: Record the experiment results using the parameters in the following

table. The first row is an example.

Addr Instruction Hits (%) Misses (%) Block

0139 LDB1, R00 50 50 2

Step 2: Analyse the experiment results and report your observation

Step 3: Calculate the miss rate and Average Memory Access Time (AMAT)

Pipelining and increase in throughput

Consider the analogy of the Mama chapati kitchen, which breaks the process of

cooking and serving chapatis in five stages. Stage 1: Receiving an Order (O), Stage

2: Kneading dough (N), Stage 3: Rolling (R) Stage 4: Cooking (C) and Serving (S).

The average time taken to serve one chapati with or without pipelining is as follows:

Without pipelining: Remember that taking an order takes 5 minites, preparing and

kneading dough takes 10 minutes, rolling takes 5 minutes, cooking takes 5 minutes

and serving takes 5 minutes.

Figure 2.5: Average time for one chapati = 120/4 = 30 minutes

87

Student’s Book Form Five

Computer Science Form 5.indd 87 23/07/2024 12:33