Page 78 - Computer_Science_F5

P. 78

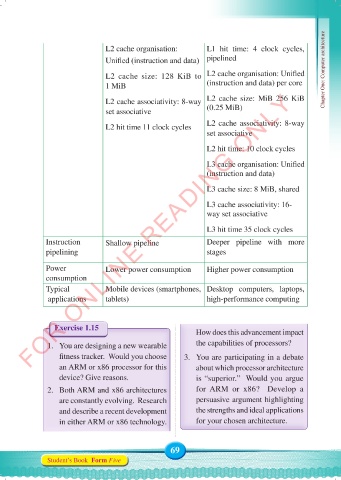

L2 cache organisation: L1 hit time: 4 clock cycles,

Unified (instruction and data) pipelined

L2 cache size: 128 KiB to L2 cache organisation: Unified Chapter One: Computer architecture

1 MiB (instruction and data) per core

FOR ONLINE READING ONLY

L2 cache associativity: 8-way L2 cache size: MiB 256 KiB

set associative (0.25 MiB)

L2 hit time 11 clock cycles L2 cache associativity: 8-way

set associative

L2 hit time: 10 clock cycles

L3 cache organisation: Unified

(instruction and data)

L3 cache size: 8 MiB, shared

L3 cache associativity: 16-

way set associative

L3 hit time 35 clock cycles

Instruction Shallow pipeline Deeper pipeline with more

pipelining stages

Power Lower power consumption Higher power consumption

consumption

Typical Mobile devices (smartphones, Desktop computers, laptops,

applications tablets) high-performance computing

Exercise 1.15

How does this advancement impact

1. You are designing a new wearable the capabilities of processors?

fitness tracker. Would you choose 3. You are participating in a debate

an ARM or x86 processor for this about which processor architecture

device? Give reasons. is “superior.” Would you argue

2. Both ARM and x86 architectures for ARM or x86? Develop a

are constantly evolving. Research persuasive argument highlighting

and describe a recent development the strengths and ideal applications

in either ARM or x86 technology. for your chosen architecture.

69

Student’s Book Form Five

Computer Science Form 5.indd 69 23/07/2024 12:32