Page 80 - Computer_Science_F5

P. 80

Why might the head chef have restricted As seen in Figure 1.63, the DMA

access to the master control panel? How controller coordinates data transfer in

does this concept translate to privileged the following manner;

instructions in computer architecture? (a) To initiate a DMA transfer, the Chapter One: Computer architecture

Provide any security risks associated processor first sends a request to the

FOR ONLINE READING ONLY

with non-privileged programs having DMA controller, specifying details

access to certain functions. like memory addresses, data size, and

transfer direction. This information

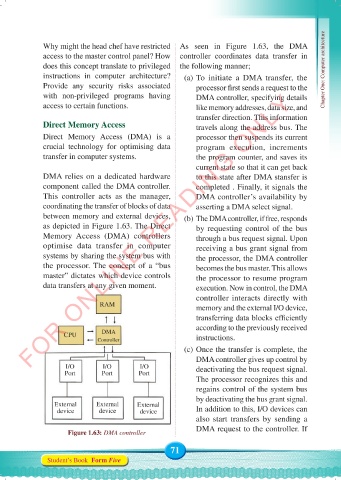

Direct Memory Access travels along the address bus. The

Direct Memory Access (DMA) is a processor then suspends its current

crucial technology for optimising data program execution, increments

transfer in computer systems. the program counter, and saves its

current state so that it can get back

DMA relies on a dedicated hardware to this state after DMA stansfer is

component called the DMA controller. completed . Finally, it signals the

This controller acts as the manager, DMA controller’s availability by

coordinating the transfer of blocks of data asserting a DMA select signal.

between memory and external devices, (b) The DMA controller, if free, responds

as depicted in Figure 1.63. The Direct by requesting control of the bus

Memory Access (DMA) controllers through a bus request signal. Upon

optimise data transfer in computer receiving a bus grant signal from

systems by sharing the system bus with the processor, the DMA controller

the processor. The concept of a “bus becomes the bus master. This allows

master” dictates which device controls the processor to resume program

data transfers at any given moment. execution. Now in control, the DMA

controller interacts directly with

RAM memory and the external I/O device,

transferring data blocks efficiently

according to the previously received

CPU DMA instructions.

Controller

(c) Once the transfer is complete, the

DMA controller gives up control by

I/O I/O I/O deactivating the bus request signal.

Port Port Port

The processor recognizes this and

regains control of the system bus

by deactivating the bus grant signal.

External External External

device device device In addition to this, I/O devices can

also start transfers by sending a

DMA request to the controller. If

Figure 1.63: DMA controller

71

Student’s Book Form Five

Computer Science Form 5.indd 71 23/07/2024 12:32