Page 81 - Computer_Science_F5

P. 81

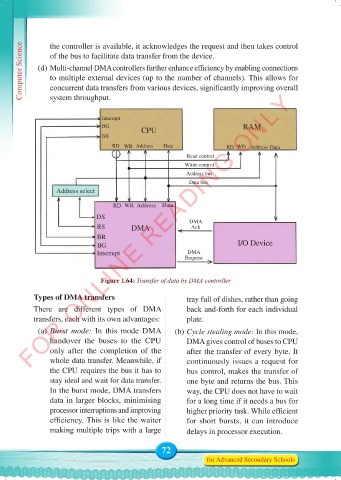

the controller is available, it acknowledges the request and then takes control

Computer Science (d) Multi-channel DMA controllers further enhance efficiency by enabling connections

of the bus to facilitate data transfer from the device.

to multiple external devices (up to the number of channels). This allows for

concurrent data transfers from various devices, significantly improving overall

FOR ONLINE READING ONLY

system throughput.

Interrupt

BG CPU RAM

BR

RD WR Address Data RD WD Address Data

Read control

White control

Address bus

Data bus

Address select

RD WR Address Data

DS DMA

RS DMA Ack

BR

BG I/O Device

Interrupt DMA

Request

Figure 1.64: Transfer of data by DMA controller

Types of DMA transfers tray full of dishes, rather than going

There are different types of DMA back and-forth for each individual

transfers, each with its own advantages: plate.

(a) Burst mode: In this mode DMA (b) Cycle stealing mode: In this mode,

handover the buses to the CPU DMA gives control of buses to CPU

only after the completion of the after the transfer of every byte. It

whole data transfer. Meanwhile, if continuously issues a request for

the CPU requires the bus it has to bus control, makes the transfer of

stay ideal and wait for data transfer. one byte and returns the bus. This

In the burst mode, DMA transfers way, the CPU does not have to wait

data in larger blocks, minimising for a long time if it needs a bus for

processor interruptions and improving higher priority task. While efficient

efficiency. This is like the waiter for short bursts, it can introduce

making multiple trips with a large delays in processor execution.

72

for Advanced Secondary Schools

Computer Science Form 5.indd 72 23/07/2024 12:32