Page 77 - Computer_Science_F5

P. 77

Computer Science simplicity makes ARM processors highly energy-efficient, making them ideal for

mobile devices like smartphones and tablets.

x86: A powerhouse for performance: Think of a heavyweight boxer with a wide

range of powerful punches. That is the x86 architecture, known for its Complex

FOR ONLINE READING ONLY

Instruction Set Computing (CISC) design. x86 offers a larger set of complex

instructions, making it a powerhouse for demanding tasks on desktops and laptops.

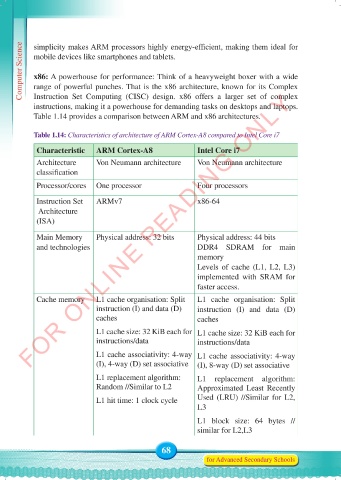

Table 1.14 provides a comparison between ARM and x86 architectures.

Table 1.14: Characteristics of architecture of ARM Cortex-A8 compared to Intel Core i7

Characteristic ARM Cortex-A8 Intel Core i7

Architecture Von Neumann architecture Von Neumann architecture

classification

Processor/cores One processor Four processors

Instruction Set ARMv7 x86-64

Architecture

(ISA)

Main Memory Physical address: 32 bits Physical address: 44 bits

and technologies DDR4 SDRAM for main

memory

Levels of cache (L1, L2, L3)

implemented with SRAM for

faster access.

Cache memory L1 cache organisation: Split L1 cache organisation: Split

instruction (I) and data (D) instruction (I) and data (D)

caches caches

L1 cache size: 32 KiB each for L1 cache size: 32 KiB each for

instructions/data instructions/data

L1 cache associativity: 4-way L1 cache associativity: 4-way

(I), 4-way (D) set associative (I), 8-way (D) set associative

L1 replacement algorithm: L1 replacement algorithm:

Random //Similar to L2 Approximated Least Recently

L1 hit time: 1 clock cycle Used (LRU) //Similar for L2,

L3

L1 block size: 64 bytes //

similar for L2,L3

68

for Advanced Secondary Schools

Computer Science Form 5.indd 68 23/07/2024 12:32