Page 112 - Computer_Science_F5

P. 112

Static multiple issue processors

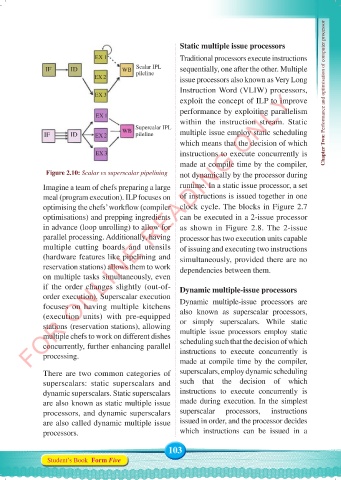

EX 1 Traditional processors execute instructions

IF ID WB Scalar IPL sequentially, one after the other. Multiple

EX 2 pileline issue processors also known as Very Long

Instruction Word (VLIW) processors,

FOR ONLINE READING ONLY

EX 3 Chapter Two: Performance and optimisation of computer processor

exploit the concept of ILP to improve

performance by exploiting parallelism

EX 1

within the instruction stream. Static

Supercalar IPL

IF ID EX 2 WB pileline multiple issue employ static scheduling

which means that the decision of which

EX 3 instructions to execute concurrently is

made at compile time by the compiler,

Figure 2.10: Scalar vs superscalar pipelining not dynamically by the processor during

Imagine a team of chefs preparing a large runtime. In a static issue processor, a set

meal (program execution). ILP focuses on of instructions is issued together in one

optimising the chefs’ workflow (compiler clock cycle. The blocks in Figure 2.7

optimisations) and prepping ingredients can be executed in a 2-issue processor

in advance (loop unrolling) to allow for as shown in Figure 2.8. The 2-issue

parallel processing. Additionally, having processor has two execution units capable

multiple cutting boards and utensils of issuing and executing two instructions

(hardware features like pipelining and simultaneously, provided there are no

reservation stations) allows them to work dependencies between them.

on multiple tasks simultaneously, even

if the order changes slightly (out-of- Dynamic multiple-issue processors

order execution). Superscalar execution

focuses on having multiple kitchens Dynamic multiple-issue processors are

(execution units) with pre-equipped also known as superscalar processors,

stations (reservation stations), allowing or simply superscalars. While static

multiple chefs to work on different dishes multiple issue processors employ static

concurrently, further enhancing parallel scheduling such that the decision of which

processing. instructions to execute concurrently is

made at compile time by the compiler,

There are two common categories of superscalars, employ dynamic scheduling

superscalars: static superscalars and such that the decision of which

dynamic superscalars. Static superscalars instructions to execute concurrently is

are also known as static multiple issue made during execution. In the simplest

processors, and dynamic superscalars superscalar processors, instructions

are also called dynamic multiple issue issued in order, and the processor decides

processors. which instructions can be issued in a

103

Student’s Book Form Five

Computer Science Form 5.indd 103 23/07/2024 12:33